The long arm of PCI Express

Monday, August 7, 2023 at 12:10PM

Monday, August 7, 2023 at 12:10PM Optical is being added as a second physical medium to the PCI Express (PCIe) data transfer protocol.

PCI Express is an electrical standard, but now the Peripheral Component Interconnect Special Interest Group (PCI-SIG) has created a working group to standardise PCIe’s delivery optically.

PCI-SIG is already developing copper cabling specifications for the PCI Express 5.0 and 6.0 standards.

Source: PCI-SIG

Source: PCI-SIG

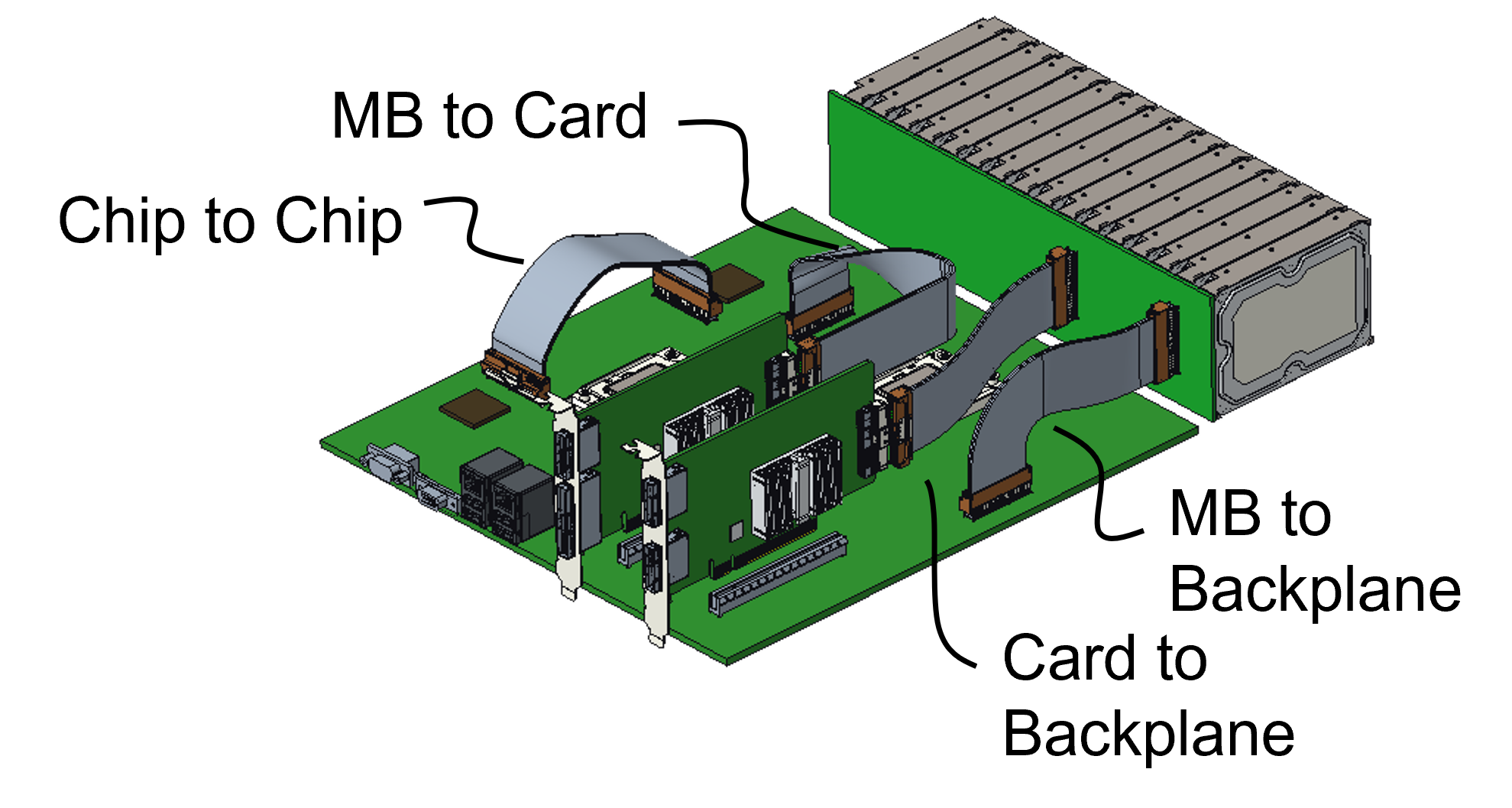

Since each generation of PCIe doubles the data transfer rate, PCI-SIG member companies want copper cabling to help with the design of high-speed PCIe interconnects on a printed circuit board (PCB), between PCBs, and between racks (see diagram).