imec's novel ADC promises faster sampling rates

Thursday, March 7, 2024 at 11:35AM

Thursday, March 7, 2024 at 11:35AM The analogue-to-digital and digital-to-analogue converters (ADCs/DACs) are like the equals sign in mathematics.

Joris Van Driessche

Joris Van Driessche

The equals sign is taught as showing two sides of an equation being the same. But really, it is a gateway between two worlds. The same applies to the ADC and DAC, which equate between the analogue and digital worlds.

Progress in wireline communications, whether client-side optics or coherent optical modems at 800 gigabits and soon 1.6 terabits, means converters must sample at higher rates.

In February, at the IEEE International Solid-State Circuits Conference (ISSCC) in San Francisco, imec detailed a proof-of-concept chip design that promises to advance high-speed ADCs.

In the paper, the authors from the Belgium nano and digital technology innovation centre detailed a 16nm CMOS 7-bit ADC test chip operating at 42 Giga-samples per second (GSps). The speed is not particularly noteworthy, but the design is: a tiny ADC circuit that promises future faster designs.

imec believes a 250-300GSps ADC will be possible when implemented in a state-of-the-art 2nm or 3nm CMOS process.

Converters for comms

Optical pluggable modules that use 4-level pulse amplitude modulation (PAM-4) use the ADC and DAC as part of the digital signal processor (DSP) chip.

Because four levels are used, PAM-4 has a reduced signal-to-noise ratio compared to non-return-to-zero signalling. A 56-gigabaud PAM-4 (112Gbps) transceiver needs to sample at 56GSps, while the converters must have an analogue bandwidth of 28GHz.

Once the next electrical speed hike at 5nm or 3nm CMOS is adopted - 112 gigabaud PAM-4 (224Gbps) - converter speeds will need to double to 112GSps with an analogue bandwidth of 56GHz.

For the long haul, the coherent DSP uses four ADCs and four DACs and different modulation schemes. Here, the symbol rate is even higher. Ciena's 3nm CMOS WaveLogic 6e has a symbol rate of 200GBd, suggesting an ADC sampling at 240-266GSps as typically the ratio is 1.2x or 1.33x the baud rate.

The recently announced OIF work to standardize 1600ZR+ will likely have a symbol rate of 260GBd. For this, an ADC sampling at over 300GSps will be needed. The OIF is expected to complete the 1600ZR+ standard in 2027.

"Coherent is being used mainly for long-reach applications. But we see that even in data centres, for 800G and 1.6T, extreme data rates are getting more challenging from a power efficiency point of view," says Joris Van Driessche, a program manager at imec in wireless and wireline communications, particularly ADCs.

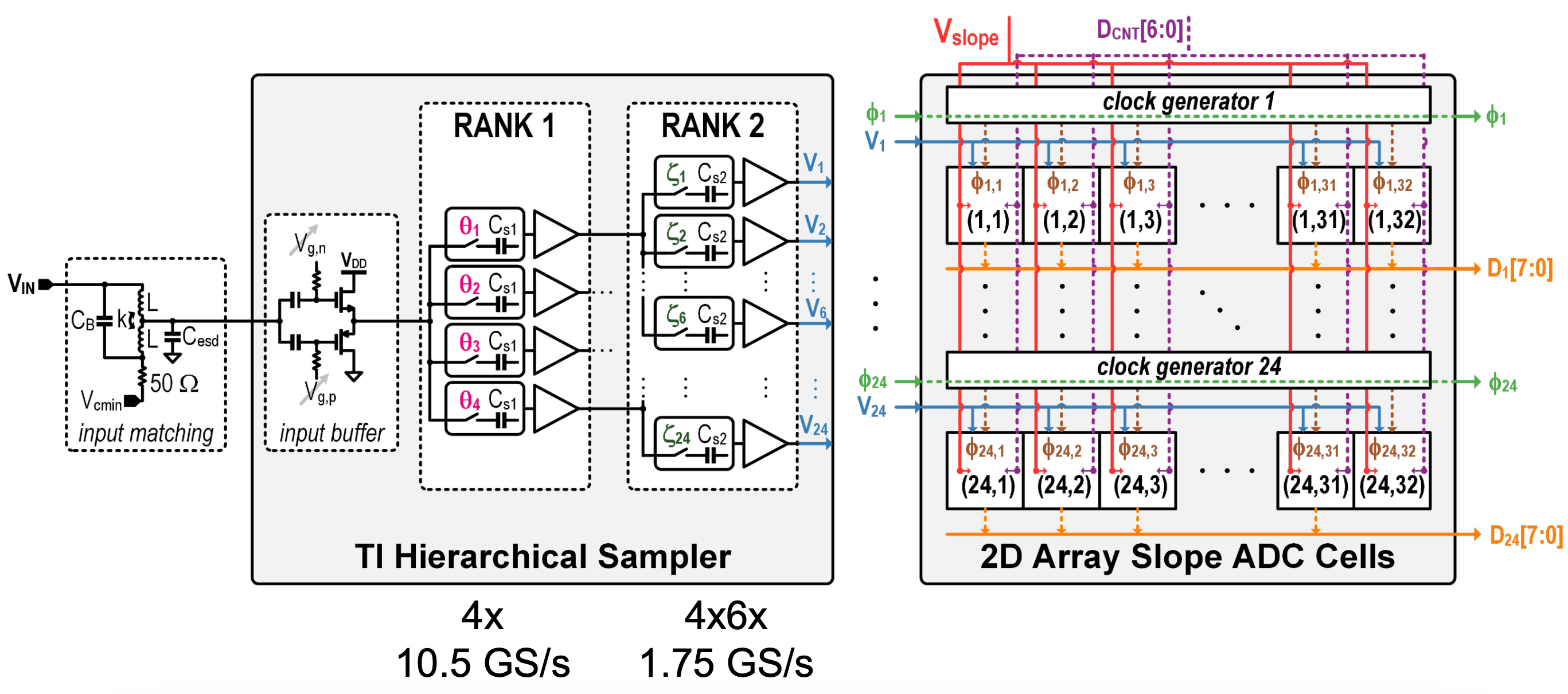

Source: imec

Source: imec

Time-interleaved SAR

For such high-speed ADCs, a time-interleaved successive approximation register (SAR) architecture is commonly used. The converter design is relatively small and power efficient. Van Driessche says imec has almost two decades of experience designing such ADCs.

The time-interleaved refers to the sampled high-speed signal being distributed across parallel ADC channels. Van Driessche cites as an example a 100GSps ADC that distributes the samples to 100 such interleaved channels, each operating at 1GSps.

"The input [to the ADC] is still operating at full speed, but your ADCs, or channels, operate at a hundredth of the speed," says Van Driessche.

The issue with a time-interleaved SAR-based converter is that as the speed increases, so does size. The result is longer interconnect lines linking the channels and distributing the clocking signal.

"Distributing the signal and the clock over long lines leads to large parasitics," says Van Driessche. And with parasitics comes a higher power consumption and/or a lower overall analogue bandwidth.

imec's ISSCC ADC (see diagram) simplifies the SAR circuitry. Dubbed a time-interleaved slope ADC, each channel is even slower than the traditional design. But the primary circuit is tiny, comprising a sampling switch, sampling capacitor, comparator, and a few digital gates. Reducing its size and arranging multiple such units in a 2D array shortens the interconnects, lowering the power and widening the circuit's bandwidth.

The result is a compact design and a much-reduced power consumption. "This is the essence: to make the core of the ADC significantly smaller, smaller than any alternative that we are aware of," says Van Driessche.

5nm CMOS design

The ISSCC paper reports the results of a 16nm test chip operating at 42GSps. "You first need to prove that it works," says Van Driessche. The core's area is 0.07mm2 only.

Now, imec is working on a 5nm CMOS version. The smaller and faster transistors help achieve higher sampling rates and better power efficiency. But it also comes with challenges: much more impact from parasitics limiting the analogue bandwidth and the resulting speed, and obtaining sufficient output voltage swing at low-power consumption for the DAC.

"The real benefit of the novel ADC architecture comes when you go to higher sampling rates," says Van Driessche. imec is not saying how fast, but it expects it to exceed 150GSps significantly. Imec expects to tape out the ADC alongside an equivalent DAC next month, with measurement results expected by year-end.

Based on simulation results, imec expects to halve the ADC's power consumption compared to other similar-speed ADCs. Designers get a notable power saving or can use two channels for the same power.

At OFC 2023, Imec detailed how it expects to achieve sampling rates of 250GSps for a 3nm CMOS coherent DSP design.

How much faster can ADCs go?

Van Driessche says that in future, the gains from technology scaling will diminish, requiring very skilled designers and a huge amount of effort.

"At some point, and I cannot say when, there will be diminishing returns," he says. "We are not there yet, but we are getting closer."

Once companies decide that a limit is reached, several parallel channels will be needed, a development designers will want to avoid for as long as possible.

Reader Comments