The OIF's coherent optics work gets a ZR+ rating

Friday, February 9, 2024 at 1:46PM

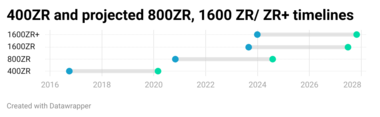

Friday, February 9, 2024 at 1:46PM The OIF has started work on a 1600ZR+ standard to enable the sending of 1.6 terabits of data across hundreds of kilometres of optical fibre.

The initiative follows the OIF's announcement last September that it had kicked off 1600ZR. ZR refers to an extended reach standard, sending 1.6 terabits over an 80-120km point-to-point link.

1600ZR follows the OIF's previous work standardising the 400-gigabit 400ZR and the 800-gigabit 800ZR coherent pluggable optics.

The decision to address a 'ZR+' standard is a first for the OIF. Until now, only the OpenZR+ Multi-Source Agreement (MSA) and the OpenROADM MSA developed interoperable ZR+ optics.