Vodafone's effort to get silicon for telco

Wednesday, May 11, 2022 at 2:44PM

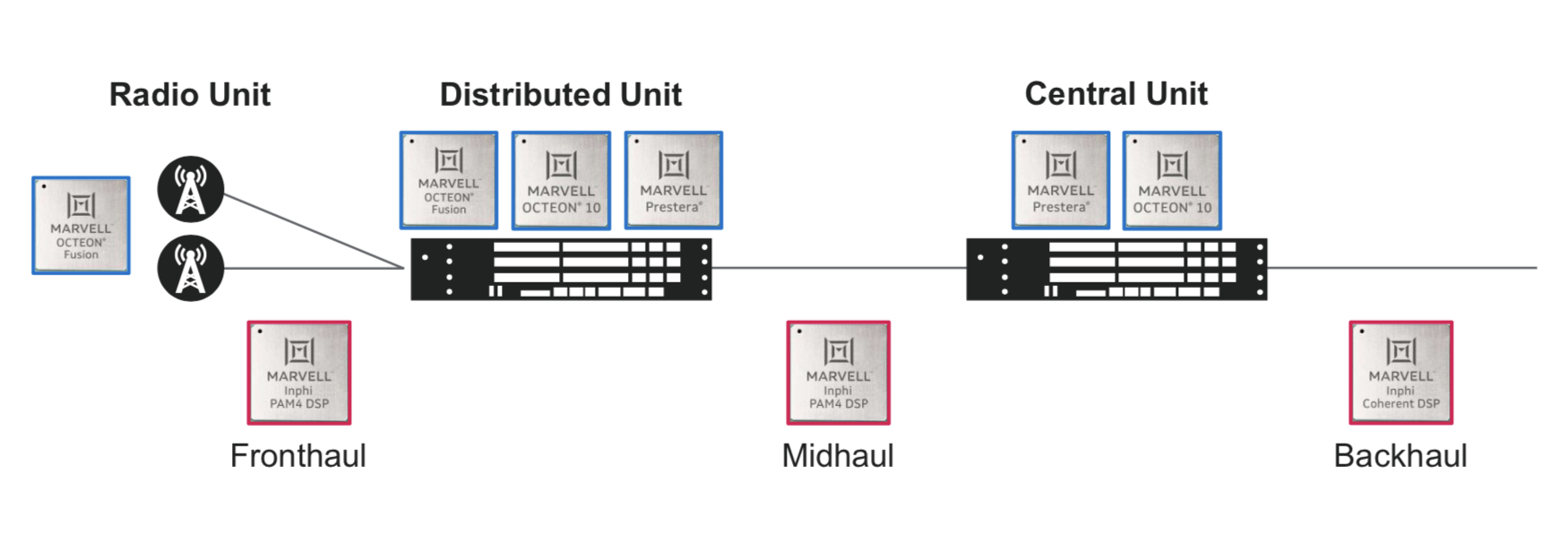

Wednesday, May 11, 2022 at 2:44PM This as an exciting time for semiconductors, says Santiago Tenorio, which is why his company, Vodafone, wants to exploit this period to benefit the radio access network (RAN), the most costly part of the wireless network for telecom operators.

The telecom operators want greater choice when buying RAN equipment.

Santiago Tenorio

Santiago Tenorio

As Tenorio, a Vodafone Fellow (the company’s first) and its network architecture director, notes, there were more than ten wireless RAN equipment vendors 15 years ago. Now, in some parts of the world, the choice is down to two.

“We were looking for more choice and that is how [the] Open RAN [initiative] started,” says Tenorio. “We are making a lot of progress on that and creating new options.”

But having more equipment suppliers is not all: the choice of silicon inside the equipment is also limited.