- Ciena has unveiled the industry’s first coherent digital signal processor (DSP) to support 1.6-terabit wavelengths

- Ciena announced two WaveLogic 6 coherent DSPs: Extreme and Nano

- WaveLogic 6 Extreme operates at a symbol rate of up to 200 gigabaud (GBd) while the Nano, aimed at coherent pluggables, has a baud rate from 118-140GBd

Part 1: WaveLogic 6 coherent DSPs

Helen Xenos

Helen Xenos

Ciena has leapfrogged the competition by announcing the industry’s first coherent DSP operating at up to 200GBd.

The WaveLogic 6 chips are the first announced coherent DSPs implemented using a 3nm CMOS process.

Ciena’s competitors are - or will soon be - shipping 5nm CMOS coherent DSPs. In contrast, Ciena has chosen to skip 5nm and will ship WaveLogic 6 Extreme coherent modems in the first half of 2024.

Using a leading CMOS process enables the cramming of more digital logic and features in silicon. The DSP also operates a faster analogue front-end, i.e. analogue-to-digital converters (ADC) and digital-to-analogue (DAC) converters.

The WaveLogic 6 matches Ciena’s existing WaveLogic 5 family in having two DSPs: Extreme, for the most demanding optical transmission applications, and Nano for pluggable modules.

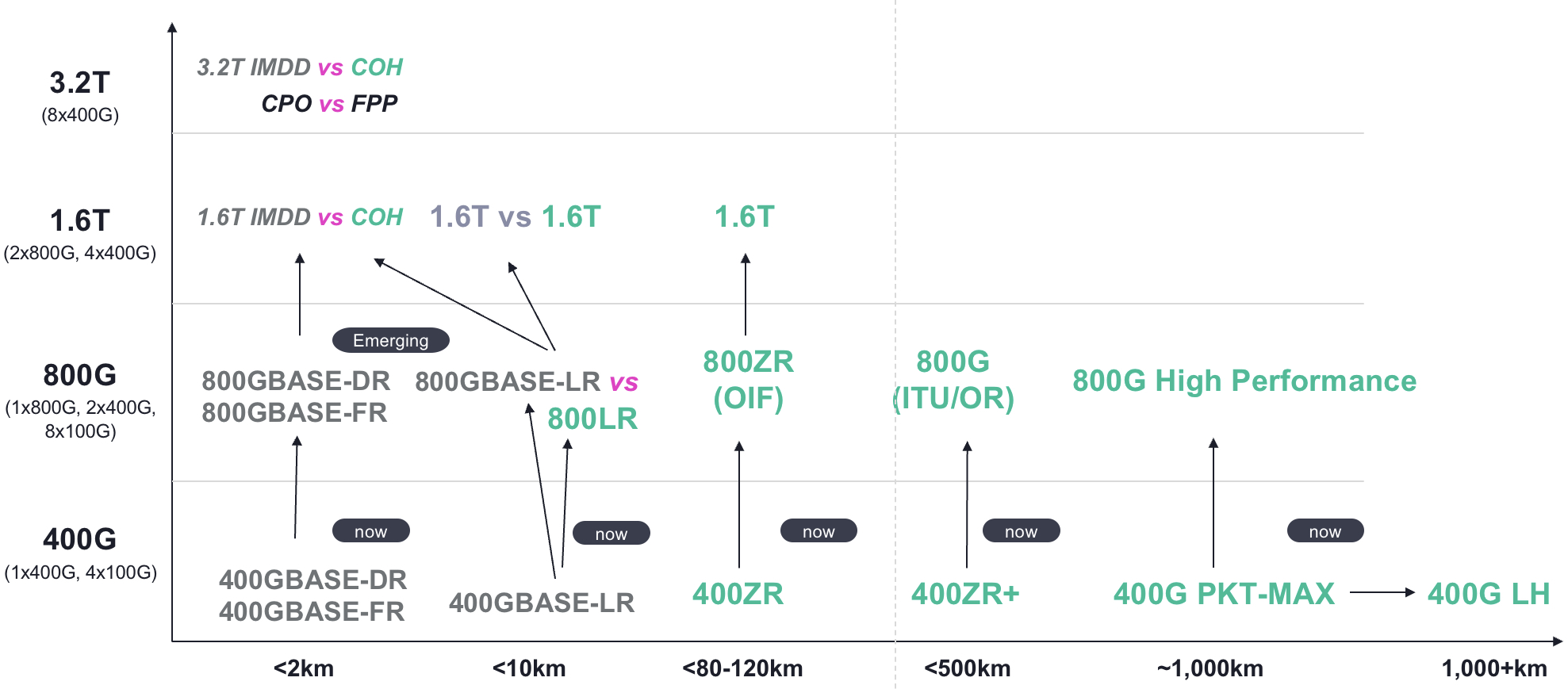

WaveLogic 6 Extreme is the first announced DSP that supports a 1.6-terabit wavelength; Acacia's (Cisco) coherent DSP supports 1.2-terabit wavelengths and other 1.2-terabit wavelength DSPs are emerging.

WaveLogic 6 Nano addresses metro-regional networks and data centre interconnect (up to 120km). Here, cost, size, and power consumption are critical. Ciena will offer the WaveLogic 6 in QSFP-DD and OSFP pluggable form factors.

Class 3.5

Network traffic continues to grow exponentially. Ciena notes that the total capacity of its systems shipped between 2010 and 2021 has grown 150x, measured in petabits per second.

Increasing the symbol rate is the coherent engineers’ preferred approach to reduce the cost per bit of optical transport.

Doubling the baud rate doubles the data sent using the same modulation scheme. Alternatively, the data payload can be sent over longer spans.

However, upping the symbol rates increases the optical wavelength's channel width. Advanced signal processing is needed to achieve further spectral efficiency gains.

One classification scheme of coherent modem symbol rate defines first-generation coherent systems operating at 30-34GBd as Class 1. Class 2 modems double the rate to 60-68GBd. The OIF’s 400ZR standard operating at 64GBd is a Class 2 coherent modem.

Currently-deployed optical transport systems operating at 90-107GBd reside between Class 2 and Class 3 (120-136GBd). Ciena’s WaveLogic 5 Extreme is one example, with its symbol rate ranging from 95-107GBd. Ciena has shipped over 60,000 WaveLogic 5 Extreme DSPs to over 200 customers.

Acacia’s latest CIM-8 coherent modem, now shipping, operates at 140GBd, making it a Class 3 design. Infinera, NEL, and Nokia announced their Class 3 devices before the OFC 2023 conference and exhibition.

Now Ciena, with its 200GBd WaveLogic 6 Extreme, sits alone between Class 3 and Class 4 (240-272GBd).

WaveLogic 6 Extreme

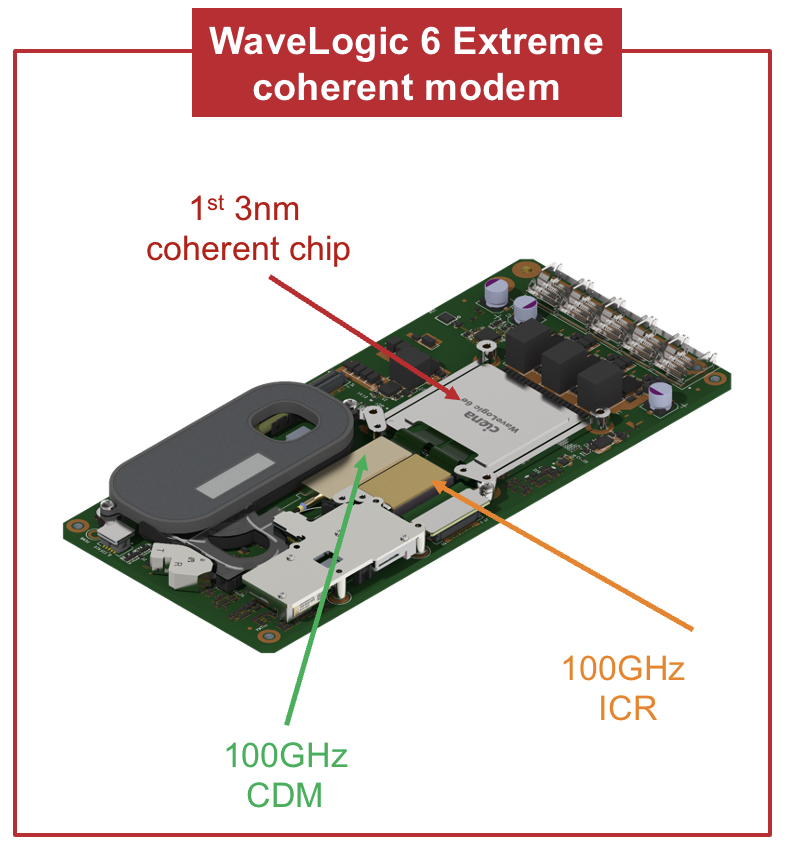

Ciena has extended the performance of all the components of the Extreme-based coherent modem to work at 200GBd.

These components include the DSP’s analogue front-end: the ADCs and DACs, the coherent optics and the modulator drivers and TIAs. All must operate with a 100GHz bandwidth.

To operate at 200GBd, the ADCs and DACs must sample over 200 giga-samples a second. This is pushing ADC and DAC design to the limit.

The coherent modem’s optics and associated electronics must also have a 100GHz operating bandwidth. Ciena developed the optics in-house and is also working with partners to bring the coherent optics to market with a 100GHz bandwidth.

Ciena uses silicon photonics for the Extreme’s integrated coherent receiver (ICR) optics. For the coherent driver modulator (CDM) transmitter, Ciena is using indium phosphide and is also evaluating other technology such as thin-film lithium niobate.

Source: Ciena

Source: Ciena

“There are multiple options that are available and being looked at,” says Helen Xenos, senior director of portfolio marketing at Ciena.

Much innovation has been required to achieve the fidelity with 100GHz electro-optics and get the signalling right between the transmitter-receiver and the ASIC, says Xenos.

Advanced signal processing

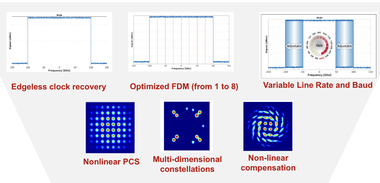

Ciena has added signal processing enhancements to improve spectral efficiency by an average of 15 per cent.

One technique is what Ciena calls edgeless clock recovery.

Source: Ciena

Source: Ciena

Ciena introduced frequency division multiplexing (FDM) sub-carriers with the WaveLogic 5 Extreme, a technique to help tackle dispersion. With the introduction of edgeless clock recovery, Ciena has created a near-ideal rectangular spectrum with sharp edges.

“First, inside this signal, there are FDM sub-carriers, but you don't see them because they are right next to each other,” says Xenos. “Getting rid of this dead space between carriers enables more throughput.”

Making the signal’s edges sharper means that wavelengths are packed more tightly, better using precious fibre spectrum. Edgeless clock recovery alone improves spectral efficiency by between 10-13 per cent, says Xenos.

Moving to 3nm allows additional signal processing. As an example, Ciena’s WaveLogic 6 Extreme DSP can select between 1, 2, 4 and 8 sub-carriers based on the dispersion on the link. WaveLogic 5 Extreme supports 4 sub-carrier FDM only.

The baud rate is also adjustable from 67-200GBd, while for the line rate, the WaveLogic 6 supports 200-gigabit to 1.6-terabit wavelengths using probabilistic constellation shaping (PCS).

Another signal processing technique used is multi-dimensional constellation shaping. These are specific modulations that are added to support legacy submarine links.

“For compensated submarine cables that have specific characteristics, they need a specialised type of design also in the DSP,” says Xenos.

Ciena also uses nonlinear compensation techniques to squeeze further performance and allow higher power signals, improving overall link performance.

Ciena can address terrestrial and new and legacy submarine links with the WaveLogic 6 Extreme running these techniques.

Xenos cites performance examples using the enhanced DSP performance of the WaveLogic 6 Extreme.

Using WaveLogic 5, an 800-gigabit wavelength can be sent at 95GBd using a 112.5GHz-wide channel. The 800-gigabit signal can cross several reconfigurable optical add-drop multiplexer (ROADM) hops.

Sending a 1.6-terabit wavelength at 185GBd over a similar link, the signal occupies a 200GHz channel. “And you get better performance because of the extra DSP enhancements,” says Xenos.

The operator Southern Cross has simulated using the WaveLogic 6 Extreme on its network and says the DSP will be able to send one terabit of data over 12,000km.

Optical transport systems benefits

Systems benefits of the Extreme DSP include doubling capacity, transmitting a 1.6-gigabit wavelength, and halving the power consumed per bit.

The WaveLogic 6 Extreme will fit within existing Ciena optical transport kit.

Xenos said the design goal is to get to the next level of cost and power reduction and maximise the network coverage for 800-gigabit wavelengths. This is why Ciena chose to jump to 3nm CMOS for the WaveLogic 6 Extreme, skipping 5nm CMOS.

WaveLogic 6 Nano

The 3nm CMOS WaveLogic 6 Nano addresses pluggable applications for metro and data centre interconnect.

“The opportunity is still largely in front of us [for coherent pluggables],” says Xenos.

The current WaveLogic 5 Nano operating between 31.5-70GBd addresses 100-gigabit to 400-gigabit coherent pluggable applications. These include fixed grid networks using 50GHz channels and interoperable modes such as OpenROADM, 400ZR and 400ZR+. Also supported is the 200-gigabit CableLabs specification.

The WaveLogic 5 Nano is also used in the QSFP-DD module with embedded amplification for high-performance applications.

There is also a new generation of specifications being worked on by standards bodies on client side and line side 800-gigabit and 1.6-terabit interfaces.

Developments mentioned by Xenos include an interoperable probabilistic constellation shaping proposal to be implemented using coherent pluggables.

The advent of 12.8-terabit and 25.6-terabit Ethernet switches gave rise to 400ZR. Now with the start of 51.2-terabit and soon 102.4-terabit switches, the OIF’s 800ZR standard will be needed.

Source: Ciena

Source: Ciena

There is also a ‘Beyond 400 Gig’ ITU-T and OpenROADM initiative to combine the interoperable OpenZR+ and the 400-gigabit coherent work of the OpenROADM MSA for a packet-optimised 800-gigabit specification for metro applications.

Another mode is designed to support not just Ethernet but OTN clients.

Lastly, there will also be long-distance modes needed at 400, 600, and 800-gigabit rates.

“With WaveLogic 6 Nano, the intent is to double the capacity within the same footprint,” says Xenos.

In addition to these initiatives, the WaveLogic 6 Nano will address a new application class for much shorter spans - 10km and 20km - at the network edge. The aim is to connect equipment across buildings in a data centre campus, for example.

Some customers want a single channel design and straightforward forward-error correction. Other customers with access to limited capacity will want a wavelength division multiplexed (WDM) solution.

The Nano’s processing and associated optics will be tuned to each application class. "The engineering is done so that we only use the performance and power required for a specific application,” says Xenos.

A Nano-based coherent pluggable connecting campus buildings will differ significantly from a pluggable sending 800 gigabits over 1,000km or across a metro network with multiple ROADM stages, she says.

The WaveLogic 6 Nano will be used with silicon photonics-based coherent optics, but other materials for the coherent driver modulator transmitter may be used.

Availability

Ciena taped out the first 3nm CMOS Extreme and Nano ICs last year.

The WaveLogic 6 Extreme-based coherent modem will be available for trials later this year. Product shipments and network deployments will begin in the first half of 2024.

Meanwhile, shipments of WaveLogic 6 Nano will follow in the second half of 2024.